VLSI Lab Presents Three Papers at the ‘Chip Olympics’

Professor Jie Gu and members of his Very Large-Scale Integration Lab team presented three papers and a live demonstration on brain-machine-interface at the premier 2024 IEEE International Solid-State Circuits Conference

Specialized to handle massive artificial intelligence (AI) workloads, AI accelerator chips are new computing hardware that are designed to perform AI tasks 100~1000X more efficiently than existing processors.

Northwestern Engineering’s Jie Gu and members of his Very Large-Scale Integration (VLSI) Lab presented three papers on applied AI chip technology at the 2024 IEEE International Solid-State Circuits Conference (ISSCC) — the foremost global forum for advances in solid-state circuits and system-on-a-chip — held February 18-22 in San Francisco.

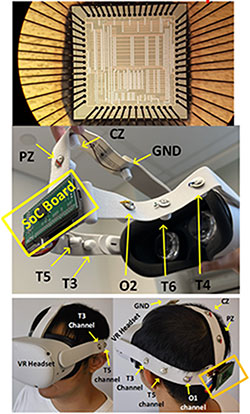

At the conference, computer engineering PhD student Zhiwei Zhong presented a live demonstration of the VLSI team’s brain-machine interface built with a novel AI-empowered neural processing system-on-a-chip (SoC). Integrated into the Meta Quest 2 virtual reality (VR) headset, the system employs user’s brainwaves to control the live scenes of a VR game or menu selections.

Zhong also presented the paper, titled “A Sub-1μJ/class Headset-Integrated Mind Imagery and Control SoC for VR/MR Applications with Teacher-Student CNN and General-Purpose Instruction Set Architecture” in the ISSCC session on intelligent neural interfaces and sensing.

Project co-authors include Gu, Lance Go, a fifth-year student pursuing a combined bachelor’s and master’s degree in computer engineering, and Texas Instruments systems engineer Yijie Wei (PhD ’23). Wei is a recipient of the 2023-2024 IEEE Solid-State Circuit Society (SSCS) Predoctoral Achievement Award.

“The chip consumes a record-low energy of 1uJ/class for convolutional neural network computation for classification of brain EEG signals,” Gu said.

Additional accepted papers

Two additional VLSI Lab papers were also accepted to ISSCC 2024.

Computer engineering PhD student Shiyu Guo presented the paper “A 28nm Physical-Based Ray-Tracing Rendering Processor for Photorealistic Augmented Reality with Inverse Rendering and Background Clustering for Mobile Devices” in the ISSCC session on processor and communication system-on-a-chip. Co-authors include Jie Gu and Sachin Sapatnekar (University of Minnesota).

The ray-tracing rendering processor was specially designed to insert photorealistic objects onto a digital photo for augmented reality applications on smartphones.

“We achieved more than 2,000-times better efficiency as compared with commercial CPUs or GPUs,” Gu said.

In addition, computer engineering PhD candidate and 2023-2024 SSCS Predoctoral Achievement Award winner Yuhao Ju presented the paper “A 28nm Physics Computing Unit Supporting Emerging Physics-Informed Neural Network and Finite Element Method for Real-Time Scientific Computing on Edge Devices” during the ISSCC machine learning accelerators session. Collaborators include Jie Gu and Ganqi Xu, a student earning a master’s degree in computer engineering.

The team developed a chip that enables high-fidelity, physics-based scientific computing on a small mobile device for real-time applications, including VR/AR, additive manufacturing, robotics, and hazard monitoring.

“The device supports the emerging physics-informed neural networks as well as the classic finite element methods,” Gu said. “The chip offers three orders of magnitude speedup versus a GPU running the same tasks.”